OrBit Project:

Board:

Ressources:

version control system:

MLL

OrBit Project:

Board:

Ressources:

version control system:

MLL

The idea behind the Core is to provide a minimal design to implement a dedicated OrBit node tailored to a specific need. For this reason, it has been deliberately limited to bare minimal peripherals and IO.

The chosen SoC is an EZR32WG330F256R61. Basically it's a Wonder Gecko with USB and a Si4461 transceiver in a single package.

There is a 4mbit SPI flash memory directly connected to the SoC used to store backup firmware and store a new firmware version for the bootloader. A part of it is also accessible by the application to store general usage data. We are looking into protecting the bootloader section, but for now it is not protected, BEWARE!

There is a 90Ω pair connected to the internal USB transceiver of the SoC. You can route it to a USB connector or anything that talk USB.

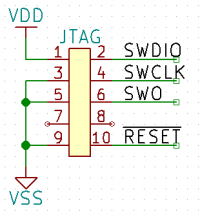

We provide all the necessary connection for a Cortex-SWD JTAG connection. The official pin-out from ARM:

Use a 50mil 2×5 header connector like this to respect the standard.

Use a 50mil 2×5 header connector like this to respect the standard.

A bootloader is present in the chip and use the external memory to store a backup image in addition to a new version that you can upload via CHOOSE A PROTOCOL.

Last version of the Schematic

The Core design is used in the Mantle board.

| PORT_B | ||||

|---|---|---|---|---|

| GPIO | Peripheral | Pin | Reserved function | Note |

| B3 | USART_2#1 | MOSI | [auxiliary memory] | <Required by core> |

| B4 | USART_2#1 | MISO | [auxiliary memory] | <Required by core> |

| B5 | USART_2#1 | SCK | [auxiliary memory] | <Required by core> |

| B6 | USART_2#1 | CS | [auxiliary memory] | <Required by core> 1) |

For more IO information and suggestion check-out the mantle board